数字电路PCB设计

基于SI的数字电路PCB高速设计

近几年来,随着集成电路工艺技术的飞速发展,使得其工作的速度越来越高。这样就带来了一个问题,体积减小使得电路的布局布线密度变大,集成电路输出开关速度变快,而同时信号工作频率不断提高,因此如何处理高速信号,保证系统设计性能成为一个设计能否成功的关键因素。

随着电子系统时钟频率迅速提高,信号边沿不断变陡,印刷电路板的线迹互连和板层特性对系统电气性能的影响也越发重要。对于低频设计,线迹互连和板层的影响可以不考虑。而当系统工作频率超过50MHz时,一方面互连关系必须考虑传输线的影响,另一方面评价系统性能也应考虑印刷电路板板材的电参数。因此,高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性(信号质量)问题。如何在系统设计以及极板设计中考虑到信号完整性的因素,并采取有效的控制措施,已经成为当今系统设计工程师和PCB设计业界中的一个热门课题。

一、确保PCB板信号完整性的方法

1.1隔离

PCB板上的器件有各种边值(edgerates)和各种容性噪声。最直接的提高信号完整性的方法是根据它们不同的边值和灵敏度,将它们在PCB上物理地隔离开来。

1.2阻抗、反射和终端负载

阻抗控制和终端负载是高速设计中的基础问题。在每个射频电路设计中也是个核心问题。然而一些数字电路运行的频率超过了射频电路,在设计中仍然没有考虑阻抗和终端负载,阻抗失配会对数字电路产生以下致命影响:

(1)数字信号将会在接受设备输入端和发射设备输出端间造成反射,反射信号被弹回并沿着线的两端传播直到最后被完全吸收;

(2)反射信号造成信号通过传输线的振铃效应,振铃将影响电压和信号时延甚至信号的完全恶化;

(3)失配信号路径可能导致信号对环境的辐射;阻抗不匹配所引发的问题可以通过终端负载来减小。通常在靠近接收器的信号线上放置一个或两个分离的终端负载,简单的做法是串接低值的排阻。终端负载限制信号的上升时间并能部分地吸收反射能量。值得注意的是终端负载并不能完全消除由于阻抗不匹配所引起的破坏性的影响。然而仔细地挑选合适的器件,终端负载可以有效地控制信号的完整性。并不是所有的布线都需要阻抗控制,这要由设计者来决定是否进行匹配。各种应用中规则是多种多样的,但一般会遵循布线长度和信号的上升时间之间的规则,即通用的对阻抗控制规则是布线长度大于上升时间的1/6时,必须进行阻抗匹配。

1.3层面和层面分割

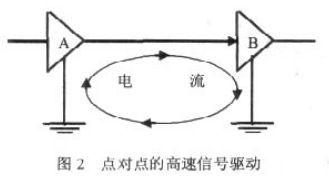

经常被数字设计者忽略的一个问题是回路的电流传播。举例来说,假设一个单向信号在两个门之间传输(如图2所示),电流会在门A到门B的回路中传播,然后通过地线连接端回到门A.,这里存在两个潜在的问题:

(1)接地应靠一个低阻抗值的路径来接。如果是用一个高阻抗值的路径,那么在图2的接地管脚就会有压降,这将会破坏所有器件对地的参考和降低输入噪声容限;

(2)电流回路所造成的回路面积尽可能小。回路就相当于天线,通常来讲,大的回路面积会增加回路辐射和导电的机会,每个PCB的设计者都希望返回的电流直接沿着信号线,这样可以得到最小的回路面积;

用大面积地线层可以同时解决上面的的问题。大面积接地在所有的接地点之间提供低阻抗,同时允许回路电流直接通过各自的信号路径传输。

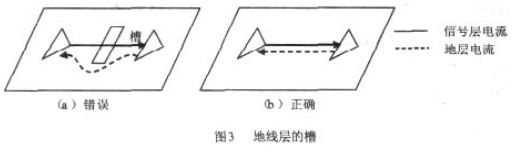

PCB设计者一个常犯的错误是在地线层开槽(如图3a所示)。图3(a)显示的是当信号线绕过地线层的开槽时的电流流向。回路电流将被迫绕过开槽,这就必然会产生大的环流回路。图3(b)显示的是地线层没有开槽时的电流流向。通常来讲,地线层不能开槽。然而也存在开槽无法避免的情况,当发生时,PCB的设计者必须保证没有任何信号路径经过开槽部分。

在带有镜像差异的电源层中也应注意层面间区域的面积,PCB的电源层和地线层在板子的边缘有辐射。从边缘辐射出来的电磁能量可能破坏临近的连接板。解决的办法是缩小电源层,使其与地线层交叠一段固定的距离。这样可以减小板外部直接区域的电磁辐射能量值,而且降低了电磁泄漏对邻近板的影响。

1.4信号布线

保证信号完整性最重要的就是信号线的物理布线。高速信号在不连续的信号线中不能传播。图4(a)所示的右转角是通常比较容易犯的有问题的布线方法,这样的布线在低频率下没有问题,如果在高频下就会辐射。要用图4(b)一个45o或图4(c)两个45度的转角来替代。

在高速电路设计中,对信号布线如果没有特别的原因,应该尽可能消除所有的短接线,短接线就如同由于信号线的阻抗失配而引发的辐射一样。另外在高速电路设计的布线中特别需要注意差分对的布线。差分对是通过两条完全互补信号线驱动的,差分对可以很好地避免噪声干扰和改进S/N率。然而差分对信号线对布线有特别高的要求:(1)两条线必须尽可能靠近布线;(2)两条线必须长度完全一致;

1.5克服串扰

在PCB设计中,串扰问题是另一个值得关注的问题当信号线间的间隔太小时,信号线间的电磁区将相互影响,从而导致信号的恶化,形成串扰。

串扰可以通过增加信号线的间距解决。然而,PCB设计者通常受制于日益紧缩的布线空间和狭窄的信号线间距,由于在设计中没有更多的选择,从而不可避免地在设计中引入一些串扰问题。文献中给出了许多可靠间距的相关规则,常用规则是3W规则,即相邻信号线间距至少应为信号线宽度的3倍。然而,实际中可接受的信号线间距依赖于实际的应用、工作环境及设计冗余等因素。因此,当串扰问题不可避免时,就应该对串扰定量化,设计者可以通过计算机仿真决定信号完整性效果和评估系统的串扰影响效果。

结论

信号完整性是贯穿于高速数字电路设计中最重要的问题之一,在此列出几种在数字电路设计中保证信号完整性的方法:(1)对灵敏元件实施与噪声器件的物理隔离;(2)阻抗控制、反射和信号终端匹配;(3)用连续的电源和地平面层;(4)布线中尽量避免采用直角;(5)差分对布线长度相等;(6)高速电路设计中应考虑串扰问题;(7)电源进行退耦处理。

在PCB板的设计过程中充分考虑到信号完整性的因素,并采取有效的控制措施,从而可以设计出安全可靠的高速电路。本文作者创新点:信号完整性(SI)问题已经成为当今PCB设计业界中一个新的热门课题。本文阐述了高速PCB电路设计中的典型信号完整性问题.描述了信号完整性问题的表现形式,着重分析了影响信号完整性的几个常见问题——串扰,电磁干扰和反射等。并有针对性地提出了解决问题的具体方案。在电路设计中,采取相应的措施能有效地提高信号完整性。

以上就是我们深圳市组创微电子有限公司为您介绍的基于SI的数字电路PCB高速设计技术。如果您有智能电子产品的软硬件功能开发需求,可以放心交给我们,我们有丰富的电子产品定制开发经验,可以尽快评估开发周期与IC价格,也可以核算PCBA报价。我们是多家国内外芯片代理商:松翰、应广、杰理、安凯、全志、realtek,有MCU、语音IC、蓝牙IC与模块、wifi模块。我们的拥有硬件设计与软件开发能力。涵盖了电路设计、PCB设计、单片机开发、软件定制开发、APP定制开发、微信公众号开发、语音识别技术、蓝牙wifi开发等。还可以承接智能电子产品研发、家用电器方案设计、美容仪器开发、物联网应用开发、智能家居方案设计、TWS耳机开发、蓝牙耳机音箱开发、儿童玩具方案开发、电子教育产品研发。

注:部分图片内容来源于网络,如有侵权,请联系删除。

- 返回顶部